北理工课题组在光量子逻辑门研究方面取得重要进展

发布日期:2023-05-29 供稿:物理学院 摄影:物理学院

编辑:王莉蓉 审核:陈珂 阅读次数:

日前,乐动(中国)物理学院张向东教授课题组与清华大学电子工程系黄翊东教授课题组张巍教授开展合作,基于反设计方法,实验实现了目前世界上最小的光量子逻辑门。相关成果以“Super-compact universal quantum logic gates with inverse-designed elements”为题发表在Science Advances期刊[Science Advances, 9, adg6685]上。该工作得到了国家自然科学基金委和国家重点研发计划的大力支持。乐动(中国)物理学院博士生何路、清华大学电子工程系博士生刘东宁为该论文的共同第一作者,乐动(中国)物理学院张向东教授、清华大学电子工程系张巍教授为论文共同通讯作者。另外,乐动(中国)张慧珍副研究员、张蔚暄研究员;清华大学刘仿教授、冯雪副教授、崔开宇副教授、学生高景行也对此工作做出了贡献。

实现通用量子计算机是量子信息科学领域的重要目标。理论上,级联一定数量的基础量子门可以实现通用量子计算机。基于此,级联控制非(CNOT)门和单比特量子门的量子光子集成回路已被广泛认为是实现大规模量子信息处理的有前途的技术。近年的工作中,人们利用多层迈克曾德尔干涉仪(MZI)成功构造了可以实现任意双量子比特处理的硅光子量子回路,但它的尺寸在毫米量级。对于数十量子比特的量子计算任务,芯片的整体尺寸需要达到晶圆级别大小。这不但对刻蚀工艺要求极高,而且也限制了芯片的使用。缩小量子逻辑门的尺寸是解决这一问题的关键。实现超紧凑的量子逻辑门是在较小的芯片尺寸下实现大规模量子计算的基础。

另一方面,在紧凑的光电子器件设计中,反设计(inverse design)方法已经显示了巨大优势。人们利用这一方法设计出了许多基本光学元件。这些反设计的器件具有比传统设计方法更好的性能和更紧凑的结构。但目前这些研究都专注于经典电磁波系统中的器件设计。例如,北理工研究团队通过使用拓扑优化方法(反设计方法中的一种),在SOI基片上曾设计并制备了目前世界最小的经典介电全光逻辑门(ACS Photonics 9, 597-604)。然而,对于光量子芯片领域,反设计方法尚未引入。这就自然产生了一个重要问题:当反设计方法应用于芯片上量子逻辑器件的设计时,是否可以做到更小的尺寸和更少的损耗?

本工作中,研究人员使用反设计方法在源集成的硅光子芯片上设计并制备出了超紧凑的通用量子逻辑门(依托天津华慧芯科技高端光电子研发工艺代工平台)。进一步,通过级联多个CNOT门和单比特量子门,研究人员也讨论了任意光量子回路的进一步扩展方法。

研究亮点之一:基于反设计方法的超紧凑单比特量子门

研究人员将量子门及辅助测试系统制备在顶硅厚度为220nm厚的SOI平台上。如图1a所示,该量子芯片由四个模块组成,分别是:(I)量子源,(II)态制备,(III)量子门和(IV)态层析模块。本研究主要关注通过反设计方法制备的超紧凑量子门,包括Hadamard门、相位z门以及CNOT门,分别如图1b-1d所示。

图1. 超紧凑量子逻辑器件及测试系统示意图

测试这些量子门的实验装置如图1e所示。在模块I中,通过片上的自发四波混频过程激发同频的两个光子,并在模块II中将其编码到两个任意路径编码的叠加态中,为测试量子门做好准备。然后,将路径编码的量子比特注入到反设计的量子门中(模块III)。输出的量子比特通过态层析的第四个模块进行投影和检测。输出的量子态通过一维光栅耦合到光纤中,并通过光纤耦合的超导纳米线单光子探测器(SNSPD)进行检测。

研究人员首先设计了单比特Hadamard 门。一般来说,在光量子芯片上,需要使用50:50的分束器(BS)来实现 Hadamard 门,其中输入量子态![]() (来自输入端口 a in )被转化为叠加态

(来自输入端口 a in )被转化为叠加态![]() 。这里 c1(c2)表示在端口 a out ( b out )的输出态

。这里 c1(c2)表示在端口 a out ( b out )的输出态![]() (

(![]() )的系数。为了进行优化过程,研究人员首先定义一个与单光子激发有关的BS目标函数

)的系数。为了进行优化过程,研究人员首先定义一个与单光子激发有关的BS目标函数![]() 。在设计过程中,随着目标函数被逐渐最大化,就可以得到优化后的结构。这个过程可以用下面的方程来描述:

。在设计过程中,随着目标函数被逐渐最大化,就可以得到优化后的结构。这个过程可以用下面的方程来描述:

![]() (1)

(1)

其中,![]() 是设计场,它表示介电常数的材料分布(在空气和Si之间),λ是波长,总目标函数是三个不同波长(λ=1520nm、1550nm和1580nm)下的目标函数之和,这是为了扩展器件工作频率的范围。此外,还应添加附加条件,即

是设计场,它表示介电常数的材料分布(在空气和Si之间),λ是波长,总目标函数是三个不同波长(λ=1520nm、1550nm和1580nm)下的目标函数之和,这是为了扩展器件工作频率的范围。此外,还应添加附加条件,即![]() ,这可以使两个端口的输出量子态的振幅平方几乎相同,从而实现50:50的分束比。

,这可以使两个端口的输出量子态的振幅平方几乎相同,从而实现50:50的分束比。

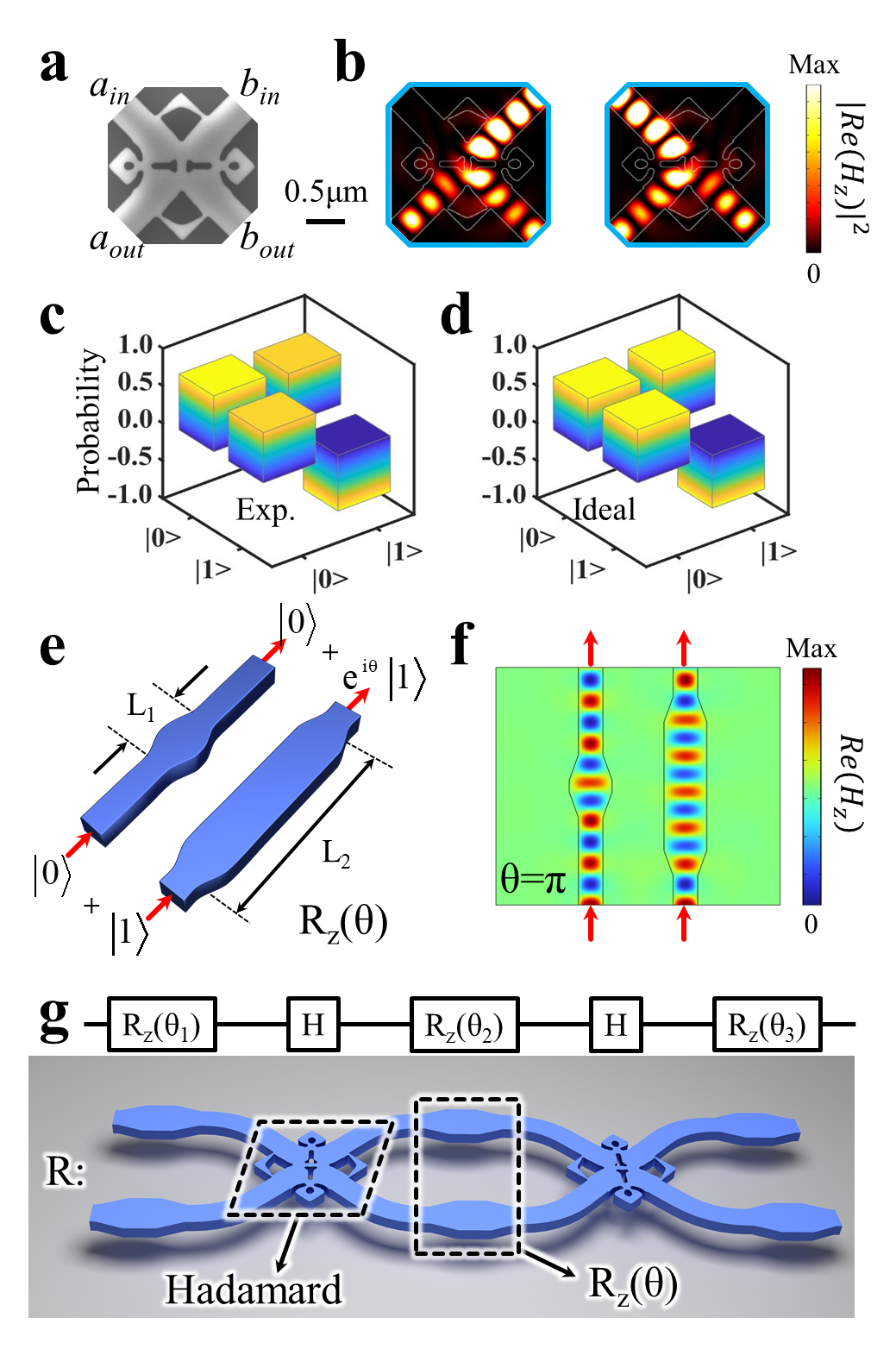

优化后的门通过电子束光刻和干法刻蚀制造,其SEM图像如图2a所示。它包含四个400nm宽的波导(分别命名为 a in 、 b in 、 a out 和 b out )和一个反设计的结构。该结构的尺寸仅为1.69μm2(1.3μm×1.3μm),小于一个真空波长。相比之下,先前的研究报道,基于定向耦合器或MMI制造的Hadamard门的尺寸约为102~103μm2,这意味着与以前的工作相比,该门的尺寸缩小了2~3个数量级。

基于单光子干涉原理,在设计的结构中可以执行Hadamard操作。当单光子态被注入到波导 a in 或 b in 中时,经过Hadamard门后,会转化为在 a out 和 b out 处输出的叠加态,并且具有π/2相位差。图2b显示了在a in 或b in 处单光子激发下的场分布的模拟结果,表明反设计的结构具有低损耗的50:50分束器的良好性能。

图2. 反设计的单比特量子门。

为了测试这样的结构是否能够执行Hadamard门的功能,研究人员对该门进行了单量子比特层析实验,如图2c所示。可以清楚地看到,输入态![]() 和

和![]() 成功地被转化为

成功地被转化为![]() 和

和![]() 。通过定量地表征Hadamard门,研究人员还计算了其保真度FH为0.987(3)。高的保真度进一步表明,Hadamard门的功能被成功实现了。

。通过定量地表征Hadamard门,研究人员还计算了其保真度FH为0.987(3)。高的保真度进一步表明,Hadamard门的功能被成功实现了。

基于这样的Hadamard门,结合相位旋转z门Rz(θ),研究人员构建了任意的单比特量子门R。对于路径编码方案,研究人员通过在光量子态的两条路径之间引入相位差轻松实现Rz(θ)门。如图2e所示,相位z门是由宽度为700nm、长度为L1和L2的加宽波导构成的。当L1≠L2时,在这些波导中的量子态![]() 或

或![]() 之间存在相位差θ。因此,相位z门可以实现。为了进一步表征Rz(θ)的性能,研究人员模拟了一个特殊情况(相位θ=π),并在图2f中展示了场分布。模拟结果表明,相位z门具有极低的损耗和精确的相位π,可以附加到量子态

之间存在相位差θ。因此,相位z门可以实现。为了进一步表征Rz(θ)的性能,研究人员模拟了一个特殊情况(相位θ=π),并在图2f中展示了场分布。模拟结果表明,相位z门具有极低的损耗和精确的相位π,可以附加到量子态![]() 上。然后,通过组合三个Rz门和两个Hadamard门,可以构造任意单比特量子门R,如图2g所示。三个Rz的相位分别为θ1、θ2和θ3,可以调整到任意的固定值。它可以将单量子比特态映射到布洛赫球上的任意点。

上。然后,通过组合三个Rz门和两个Hadamard门,可以构造任意单比特量子门R,如图2g所示。三个Rz的相位分别为θ1、θ2和θ3,可以调整到任意的固定值。它可以将单量子比特态映射到布洛赫球上的任意点。

研究亮点之二:基于反设计方法的超紧凑两比特量子门

研究人员使用线性光学方案结合反设计方法,设计并制备了两量子比特CNOT门。这种方案已在自由空间和集成光学中得到证明。CNOT门的设计可以通过将三个33:67分束器(透射率为T=0.67,反射率为R=0.33)并联实现。因此,对CNOT门的反设计就是对33:67分束器的反设计。33:67分束器的反设计过程类似于Hadamard门,但需要更改设计过程中的优化参数。所设计和制作的CNOT门如图3a所示。CNOT门的制作过程也类似于Hadamard门。33:67分束器之间的距离为500nm,以确保其中的量子态不会相互影响。CNOT门的宽度为6.4μm,深度为1.3μm(小于一个真空波长)在量子态传播的方向上。据研究人员所知,这里设计的CNOT门的尺寸(8.32μm2)是目前世界上最小的。

图3. 反设计CNOT门及其实验结果和理论结果。

在设计的CNOT门中,有六个输入和输出波导,从上到下依次命名为第1到第6条波导。为方便起见,这些输入波导中的量子态被定义为![]() 、

、![]() 、

、![]() 、

、![]() 、

、![]() 和

和![]() 。图3b显示了当这些单光子态(λ=1550nm)分别注入波导时的模拟场分布。可以看到,该器件具有良好的性能,可实现33:67分束器的功能,并且其损耗小,彼此之间没有串扰耦合。

。图3b显示了当这些单光子态(λ=1550nm)分别注入波导时的模拟场分布。可以看到,该器件具有良好的性能,可实现33:67分束器的功能,并且其损耗小,彼此之间没有串扰耦合。

为了实现CNOT门的功能,研究人员首先考虑在ZZ基下测量CNOT门功能。为了表征CNOT门的性能,研究人员测量了每个输入态的输出概率。在图3c中,对所有输入态,研究人员测量了投影到不同输出态的符合计数,并对其进行归一化处理,得到输入输出概率。相应的理论结果显示在图3d中。通过比较两者,可以发现实验结果与理论吻合良好。此外,通过计算,可以得到CNOT门的保真度为FZZ=0.9481±0.0064。接下来,研究人员还测试了该门在XX基下的逻辑功能。实验结果(图3e)与理论(图3f)数据吻合良好。另外,研究人员也计算了XX基下的平均变换保真度Fxx=0.9445±0.0051。在ZZ和XX基下的高保真度定量地证明了该门实现了量子CNOT功能。

CNOT 门的一个重要功能是可以将两个量子态纠缠在一起。在特定情况下,可以通过输入叠加态![]() 和

和![]() (

(![]() )来生成最大纠缠的贝尔态

)来生成最大纠缠的贝尔态![]() 、

、![]() 、

、![]() 和

和![]() 。在实验中,四个贝尔态都被准确地生成了,如图3g-3n。相应保真度分别为0.9034±0.0110,0.9634±0.0059,0.9578±0.0068和0.9382±0.0067,这证明了该门良好的纠缠能力。为了充分表征反设计的CNOT门,研究人员还进行了量子过程层析。通过实验数据处理,进一步得到了CNOT门的量子过程保真度Fexp=0.9080±0.0030。

。在实验中,四个贝尔态都被准确地生成了,如图3g-3n。相应保真度分别为0.9034±0.0110,0.9634±0.0059,0.9578±0.0068和0.9382±0.0067,这证明了该门良好的纠缠能力。为了充分表征反设计的CNOT门,研究人员还进行了量子过程层析。通过实验数据处理,进一步得到了CNOT门的量子过程保真度Fexp=0.9080±0.0030。

研究亮点之三:基于反设计方法的超紧凑光量子回路

量子门的主要应用之一是构建集成光量子回路,来实现任意的量子过程。因此,证明所设计的反设计量子门可以用于构建具有超紧凑尺寸的量子回路具有重要意义。如图4a所示的示意图,任意的两量子比特量子回路可以由三个反设计的CNOT门和八个任意的R门组成。这样一个量子回路的尺寸约为103 μm2。与以前的工作相比,尺寸缩小了4个数量级,从107μm2缩小到103 μm2。这意味着超过104个2量子比特量子回路可以集成到相同的区域。

图4. 反设计超紧凑量子回路的方案。

为了测试所设计的超紧凑量子回路的功能,研究人员进行了单光子态演化的数值模拟。图4b和图4d展示了单光子态从第一个和第二个波导激发的概率幅的平方。从第一到第四个波导的输出态的相应的概率幅平方标记为图4c和图4e中的红线。同时,这四个波导的输出叠加态的概率幅的平方的理论结果被标记为图中的蓝色矩形。比较这些结果,可以发现理论和数值模拟之间的一致性很好,这表明即使将量子回路集成到如此小的尺寸中,量子回路的功能也可以很好的被执行。

研究人员使用反设计方法在集成源的硅光子芯片上设计并制造了超紧凑的通用量子逻辑门。CNOT门和Hadamard门的尺寸分别只有8.32μm2(1.3μm×6.4μm)和1.69μm2(1.3μm×1.3μm),它们是目前报道的最小的光量子门。基于这些通用量子逻辑门,研究人员还设计了用于实现任意两量子比特信息处理的硅光子量子回路。相比之前的量子光子回路,这个回路的尺寸缩小了4个数量级。这些超紧凑量子门和回路的高性能效率也已经得到了证明。这项工作为芯片集成的量子信息处理提供了新思路。

论文链接1:https://www.science.org/doi/10.1126/sciadv.adg6685

论文链接2:https://doi.org/10.1021/acsphotonics.1c01569

分享到: